# ZG2100M/ZG2101M Wi-Fi<sup>®</sup> Module Data Sheet

2.4 GHz 802.11b Low Power Transceiver Module

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. -Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip -intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-064-5

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### 2.4 GHz 802.11b Low Power Transceiver Module

# Utility and Smart Energy

- Thermostats

- Smart Meters

- White Goods

- HVAC

# **Consumer Electronics**

- Remote Control

- Internet Radio

- Home Security

- Toys

# Industrial Controls

- Chemical Sensors

- HVAC

- Security Systems

- M2M

Communication

# Remote Device Management

- Location and Asset Tracking

- Automotive

- Code Update

### Retail

- POS TerminalsWireless Price Tags

- Digital Remote Signage

# Medical, Fitness, and Healthcare

- Glucose Meters

- Fitness Equipment

- Patient Asset Tracking

### **Features**

- Single-chip 802.11b including MAC, baseband, RF and power amplifier

- Data Rate: 1 & 2 Mbps

- 802.11b/g/n compatible

- Low power operation

- API for embedded markets, no OS required

- PCB or external antenna options

- Hardware support for AES and RC4 based ciphers (WEP, WPA, WPA2 security)

- SPI slave interface with interrupt

- Single 3.3V supply, operates from 2.7V to 3.6V (see section 5)

- 21mm x 31mm 36-pin Dual Flat pack PCB SM Package

- Wi-Fi Certified, RoHS and CE compliant

- FCC Certified (USA, FCC ID: W7O-ZG2100-ZG2101)

- IC Certified (IC: 8248A-G21ZEROG)

- Fully compliant with EU & meets the R&TTE Directive for Radio Spectrum

- Radio Type Approval Certified (Japan, ZG2100M based solution ID: AC164136-2 005WWCA0311 005GZCA0149)

# **Description**

The ZG2100M & ZG2101M modules are low-power 802.11b implementations. All RF components, the baseband and the entirety of the 802.11 MAC reside on-module, creating a simple and cost-effective means to add Wi-Fi connectivity for embedded devices. The module(s) implement a high-level API, simplifying design implementation and allowing the ZG2100M or ZG2101M to be integrated with 8- and 16-bit host microcontrollers. Hardware accelerators support the latest Wi-Fi security standards.

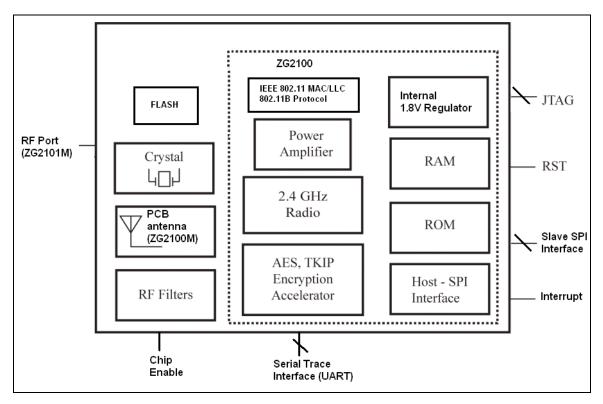

Figure 1: ZG2100M/ZG2101M Module: Functional Block Diagram

DS70624A – page 4 © 2010 Microchip Technology

# **Table of Contents**

| 1.  | 1. Key Features                                               | 6  |  |  |  |

|-----|---------------------------------------------------------------|----|--|--|--|

| 2.  | Detailed Description                                          | 7  |  |  |  |

|     | 2.1 Overview                                                  | 7  |  |  |  |

|     | 2.2 Supply Blocks and Boot-Up Sequence for Single 3.3V Supply | 7  |  |  |  |

|     | 2.3 ZG2100 Power States                                       | 9  |  |  |  |

|     | 2.4 Electrostatic discharge (ESD)                             | 10 |  |  |  |

|     | 2.5JTAG Interface                                             | 10 |  |  |  |

|     | 2.6 Serial Interface for Trace                                | 10 |  |  |  |

|     | 2.7 SPI Interface                                             | 10 |  |  |  |

|     | 2.7.1 SPI Slave Interface with Interrupt for Host Operation   | 10 |  |  |  |

|     | 2.7.2 Host-Control SPI Interface                              | 10 |  |  |  |

|     | 2.7.3 SPI Timing Characteristics                              | 11 |  |  |  |

|     | 2.7.4 SPI Timing                                              | 12 |  |  |  |

|     | 2.7.5 SPI Register Access                                     | 13 |  |  |  |

|     | 2.8 FIFO Interface                                            | 14 |  |  |  |

|     | 2.8.1 FIFO Read                                               | 14 |  |  |  |

|     | 2.8.2 FIFO Write                                              | 15 |  |  |  |

|     | 2.9 Fully-Integrated Radio                                    |    |  |  |  |

|     | 2.10 Internal ROM/RAM/NVM                                     | 15 |  |  |  |

|     | 2.11 Hardware Support for AES and TKIP                        | 15 |  |  |  |

| 3.  | ZG2100M/ZG2101M Pin-Out and Function                          | 16 |  |  |  |

| 4.  | Package Information                                           |    |  |  |  |

|     | 4.1 Module Drawing                                            |    |  |  |  |

|     | 4.2 Module Layout Guidelines                                  |    |  |  |  |

|     | 4.3 Module Use Schematic                                      | 21 |  |  |  |

| 5.  | Electrical Characteristics                                    | 23 |  |  |  |

|     | 5.1 Power Consumption                                         | 23 |  |  |  |

| 6.  | Radio Characteristics                                         | 25 |  |  |  |

|     | 6.1 Transmitter 2.4GHz Band                                   | 25 |  |  |  |

|     | 6.2 Receiver 2.4GHz Band                                      | 25 |  |  |  |

| 7.  | Digital Electrical Characteristics                            | 26 |  |  |  |

| 8.  | Module Reflow Profile                                         | 27 |  |  |  |

| 9.  | Ordering Information                                          | 28 |  |  |  |

| 10. | Regulatory Notes                                              | 29 |  |  |  |

| 11  | Revision History                                              | 31 |  |  |  |

# 1 Key Features

# **Ease of Software Development**

- Simple API suited for embedded market

- Targeted for low resource host processors

- Entire MAC integrated on-chip

- Serialized MAC address, each device comes with an unique MAC address in range 001EC0xxxxxx

- · Simple usage model, no requirement for OS

# **Low Power Operation**

- Low power, 250uA sleep mode with fast wake up, 0.1uA hibernate,

- Sleep power state managed by ZG2100, enabling low average power while maintaining AP association without host control

- Battery operable from 2.7v to 3.6v (see power specs for limitations)

### RF

- Integrated PA

- Support for external PA for high RF output power applications

- Power output +10dBm typical at antenna

- Power output programmable from +0dBm to meet varying application needs

- Min RX sens.of-91dBm @ 1MB/Sec. at antenna

- Integrated PCB antenna (ZG2100M)

- Support for external antenna available (ZG2101M)

# **Low External Component Count**

- Fully integrated RF frequency synthesizer, reference clock, and Integrated PA

- Single 3.3V supply

# Wi-Fi & Regulatory

- Supports 1Mbps & 2Mbps and module-based solutions are "Wi-Fi certified" for 802.11b

- Hardware support for AES, and RC4 based ciphers (WEP, WPA, WPA2 security)

- FCC Certified (USA, FCC ID: W7O-ZG2100-ZG2101), IC Certified (IC: 8248A-G21ZEROG), Radio Type Approval Certified (Japan, ZG2100M based solution ID: AC164136-2 005WWCA0311 005GZCA0149, Wi-Fi Certified, RoHS and CE compliant, and fully compliant with European Market and meet the R&TTE Directive for Radio Spectrum

# 2. Detailed Description

### 2.1 Overview

The ZG2100 single-chip 802.11b transceiver includes MAC, baseband, RF and power amplifier, and built in hardware support for AES, and TKIP (WEP, WPA, WPA2 security). The device has an API targeted for embedded markets so an operating system is not required for operation. There is a fully integrated radio ideal for 1 & 2Mbps operation with optional support for external PA and antenna switch operation.

The ZG2100M modules incorporate the ZeroG ZG2100 single chip 802.11b transceiver with all associated RF components, crystal oscillator, and bypass and bias passives along with a printed antenna to provide a fully integrated Wi-Fi I/O solution controllable from an 8 or 16-bit processor. The ZG2101M module is similar but bypasses the on-board PCB antenna and uses a U.FL connector for connection to an external antenna.

Interface is via SPI slave interface with interrupt for HOST operation. The modules support RS232 serial interfaces (requires level shifter) for debug and JTAG boundary scan. Operation is via a single 3.3V supply, supporting various power states, such as hibernate and SLEEP, for end applications long battery life. ZG2100M contains a built in PCB antenna for ease of system integration and significant BOM reduction.

The module is manufactured on an FR4 PCB substrate, with components on the top surface only. Connection is made as a surface mount component via flat pack (no pin) connections on two sides.

# 2.2 Supply Blocks and Boot-Up Sequence for Single 3.3V Supply

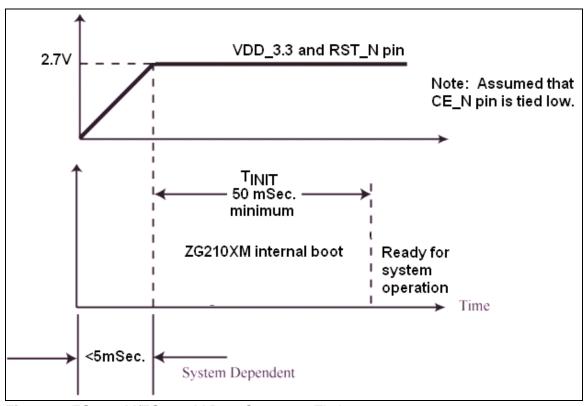

The internal regulators for the digital and analog core power supplies are enabled by keeping the chip enable pin (CE\_N) low. The waveforms for the core supplies, illustrated on the following page, as shown when powering up the ZG2100M/ZG2101M with a nominal 3.3V applied to VDD\_3.3. There is an internal power-on-reset detect which starts the boot sequence from the internal ROM when the core supply (VDD\_1.8) is up. After approximately 50 ms from when VDD\_3.3 supply is within specification, the ZG2100M/ZG2101M is ready for operation.

**Figure 2:** ZG2100M/ZG2101M Boot Sequence Timing. Refer to Section 4.1 Electrical Characteristics, Note 1.

DS70624A – page 8 © 2010 Microchip Technology

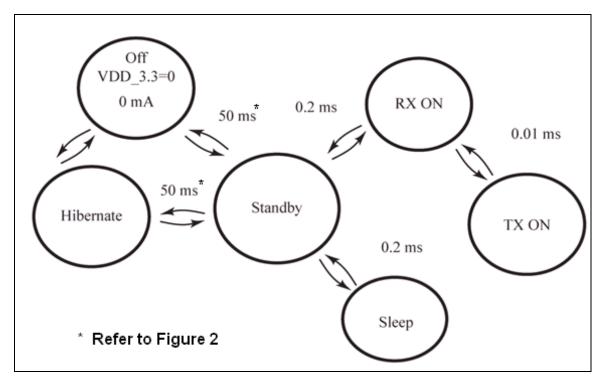

# 2.3 ZG2100 Power States

The power state definitions are as follows:

|           | VDD_3.3 | CE_N | Circuitry                                          |

|-----------|---------|------|----------------------------------------------------|

| OFF       | 0V      | 0V   | Power disconnected to ZG2100                       |

| HIBERNATE | 3.3V    | 3.3V | All internal circuitries are OFF                   |

| SLEEP     | 3.3V    | 0V   | Reference clock and internal bias circuitry are ON |

| RX ON     | 3.3V    | 0V   | Receive circuits are ON                            |

| TX ON     | 3.3V    | 0V   | Transmit circuits are ON                           |

| STANDBY   |         |      | Transition State Only                              |

Figure 3: ZG2100M/ZG2101M Power State Diagram

# 2.4 Electrostatic discharge (ESD)

The ZG2100 IC, integrated within the ZG2100M/ZG2101M, has passed ESD HBM JEDEC Standard No. 22-A114 / 2000 Volts and ESD CDM JEDEC Standard No. 22-C101 / 500V all pins. Users must exercise ESD handling precautions when working with the product either in component form, or exposed PCBs.

### 2.5 JTAG Interface

Joint Test Action Group (JTAG) is the common name used for the IEEE 1149.1 standard entitled Standard Test Access Port and Boundary-Scan Architecture for test access ports used for testing printed circuit boards using boundary scan. ZG2100M/ZG2101M supports JTAG boundary scan. JTAG\_EN and JTAG\_RST\_N need to be driven HIGH to enable JTAG mode.

#### 2.6 Serial Interface for Trace

ZG2100M/ZG2101M incorporates Transmitted Data pin (UART0\_TX) and Received Data pin (UART0\_RX) for serial testing purposes. These pins can be connected to commercially available RS-232 line drivers/ receivers with appropriate external level shifters. The ZG2100 serial interface is fully tested at 115200 bits/seconds baud rate with RS232/UART interface applications.

### 2.7 SPI Interface

# 2.7.1 SPI Slave Interface with Interrupt for Host Operation

The slave Serial Peripheral Interface Bus (SPI) is used to interface with the HOST. The slave SPI interface works with ZG2100M/ZG2101M Interrupt line (INT\_NX). When data is available for the HOST during operation, the INT\_NX line is asserted low by ZG2100. The INT\_NX line is de-asserted high, by ZG2100M/ZG2101M, after the data is transferred to the HOST SPI buffer. The SPI CLK Speed can be up to 25MHz.

#### 2.7.2 Host-Control SPI Interface

The slave SPI interface implements the [CPOL=0; CPHA=0] and [CPOL=0; CPHA=1] modes (0 and 3) of operation. That is, data is clocked in on the first rising edge of the clock after Chip Select goes valid.

Data on the bus is required to be big endian, with most significant bit on the bus first and least significant bit going last. There are two decode regions. One for register access and one for a FIFO interface. Operation for both regions is shown below. The INT\_NX signal allows interrupts to be signaled to the host device.

As an example of any 32-bit register access, suppose a write to register 0xF0\_0F18 is desired:

Write to host register 0x38 with addr[31:16] (0x00f0). 24 bit transaction.

Write to host register 0x39 with addr[15:0] (0x0F18). 24 bit transaction.

Write to host register 0x3a with data[31:16]. 24 bit transaction.

Write to host register 0x3b with data[15:0]. 24 bit transaction.

Write to host register 0x37 with a byte that has the following pattern: 8 bit transaction

[7:4] byte enables (active high for the valid bytes that you want to write in steps 3 and 4).

[3:0] - 4'b0001 -> activate write to register

#### For a read of 0xF0 0D00:

Write to host register 0x38 with addr[31:16] (0x00F0). 24 bit transaction.

Write to host register 0x39 with addr[15:0] (0x0F18). 24 bit transaction.

Write to host register 0x37 with a byte that has the following pattern: 8 bit transaction

[7:4] byte enables (active high for the valid bytes that you want to read in steps 1 and 2).

[3:0] - 4'b0011 -> active read of register

Read host register 0x3a to get data [31:24] 24 bit transaction

Read host register 0x3b to get data [15:0] 24 bit transaction

Each of the steps above is a single SPI transaction; the chip select (CE\_N) is active low during each step.

# 2.7.3 SPI Timing Characteristics

| Characteristic                    | Min  | Max    |

|-----------------------------------|------|--------|

| SPI, Data setup to falling clock  | 1 ns |        |

| SPI, Data hold from falling clock | 1 ns |        |

| SPI SLAVE CLK                     |      | 25 MHz |

| SPI MASTER CLK                    |      | 25 MHz |

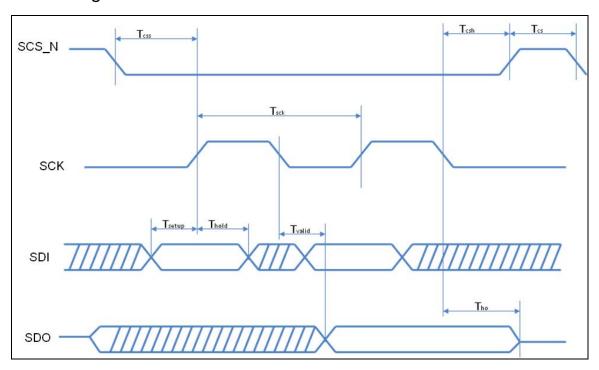

Figure 4: ZG2100M/ZG2101M SPI Timing Characteristics

# 2.74 SPI Timing

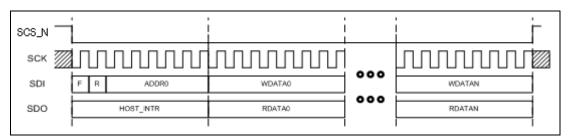

Figure 5: ZG2100M/ZG2101M SPI Timing Waveform

| Symbol | Parameter        | Min   | Тур | Max   |

|--------|------------------|-------|-----|-------|

| Tsck   | SCK Clock Period | 40 ns |     |       |

| Tcs    | SCS_N High Time  | 50 ns |     |       |

| Tcss   | SCS_N Setup Time | 50 ns |     |       |

| Tcsh   | SCS_N Hold Time  | 50 ns |     |       |

| Tsetup | SDI Setup Time   | 10 ns |     |       |

| Thold  | SDI Hold Time    | 10 ns |     |       |

| Tvalid | Output Valid     |       |     | 15 ns |

| Tho    | Output Hold Time | 0     |     | 15 ns |

Figure 6: ZG2100M/ZG2101M SPI Timing Data

DS70624A – page 12 © 2010 Microchip Technology

# 2.7.5 SPI Register Access

Figure 7: ZG2100M/ZG2101M SPI Register Access

**F** is a select between FIFO space and register space. If this bit is a 1, the data FIFO space is selected. If this bit is a 0, the register address space is selected.

**R** is the Read/Write bit. If this bit is a 1, the operation is a read. If this bit is a 0, the operation is a write

**ADDR0** is the starting address for the transaction. This value is only used for register accesses and is ignored during FIFO accesses.

**WDATAn** is the write data byte. This is only used from write operations and is ignored during read operations.

**RDATAn** is the read data byte. This is always valid for both, read and write operations. If contains the current value of any register location.

**HOST\_INTR** is the 8-bit interrupt register.

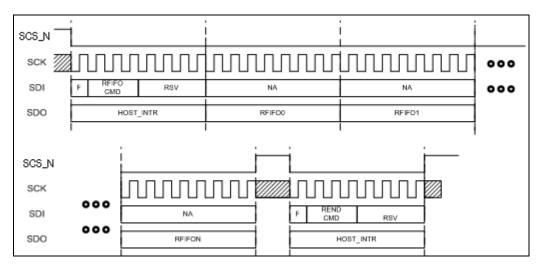

# 2.8 FIFO Interface

**HOST FIFO Basic Commands**

FCMD[2:0]

0x0 - RFIFO\_CMD

0x1 - WCONT (Continue Previous Packet)

0x2 - WSTART0 (Start Packet, head/continue)

0x3 - WSTART1 (Start Packet, head0/continue)

0x4 - WEND CMD

0x5 - REND CMD

### 2.8.1 FIFO Read

Figure 8: ZG2100M/ZG2101M FIFO Read Timing

#### SCS\_N سسسس SDI WDATAG WDATA1 000 SDO HOST\_INTR HOST\_INTR HOST\_INTR 000 SCS\_N SCK SDI WDATAN 000 000 SDO HOST\_INTR HOST\_INTR 000 000 SCS\_N SCK SDI WDATAN 000

#### 2.8.2 FIFO Write

SDO

Figure 9: ZG2100M/ZG2101M FIFO Write Timing

HOST INTR

# 2.9 Fully-Integrated Radio

000

ZG2100M/ZG2101M incorporates a fully integrated radio Ideal for 1 & 2 Mbps operation with optional support for external PA operation. The direct conversion TX design incorporates an integrated PA, with up to +10dBm typical at antenna, and fully integrated internal power control loop. The direct conversion RX chain utilizes Automatic Gain Control that allows ZG2100M/ZG2101M to receive with a minimum input Level sensitivity (1Mbps @ <8% PER) of -91 dBm typical at the antenna. The ZG2100M/ZG2101M only needs an external crystal for a reference clock.

HOST INTR

# 2.10 Internal ROM/RAM/NVM

ZG2100M/ZG2101M incorporates internal ROM, RAM, and NVM. The internal ROM and RAM are reserved only for ZG2100M/ZG2101M operations. The NVM holds information such as the MAC address, TX manufacturing calibration values, and frequency calibration values.

# 2.11 Hardware Support for AES and TKIP

ZG2100M/ZG2101M supports Wi-Fi encryption methodology (AES and RC4 based ciphers).

# 3. ZG2100M/ZG2101M Pin-Out and Function

| Pins | Name       | Internal<br>Bias | Required<br>Bias Resistor | Description                                                     |

|------|------------|------------------|---------------------------|-----------------------------------------------------------------|

| 1    | GND        |                  |                           | Ground                                                          |

| 2    | VDD_1.8    |                  |                           | See below                                                       |

| 3    | JTAG_TDO   | Н                |                           | JTAG data out                                                   |

| 4    | JTAG_TCK   |                  | Constant drive            | JTAG Clock in                                                   |

| 5    | JTAG_TMS   | Н                |                           | JTAG Mode in                                                    |

| 6    | JTAG_TDI   | Н                |                           | JTAG data in                                                    |

| 7    | RST_N      |                  | Constant drive            | Chip reset in                                                   |

| 8    | DNC        |                  |                           | Do Not Connect                                                  |

| 9    | JTAG_RST_N |                  | Constant drive            | JTAG Reset in, pulling this pin low will keep JTAG idle (reset) |

| 10   | GND        |                  |                           | Ground                                                          |

| 11   | VDD_1.8    |                  |                           | See below                                                       |

| 12   | DNC        |                  |                           | Do Not Connect                                                  |

| 13   | DNC        |                  |                           | Do Not Connect                                                  |

| 14   | DNC        |                  |                           | Do Not Connect                                                  |

| 15   | DNC        |                  |                           | Do Not Connect                                                  |

| 16   | RES        |                  | Pull-down                 | FLASH Write Protect. See below.                                 |

| 17   | VDD_3.3    |                  |                           | 3.3V Power                                                      |

| 18   | GND        |                  |                           | Ground                                                          |

| 19   | GND        |                  |                           | Ground                                                          |

| 20   | CE_N       |                  |                           | Chip enable in                                                  |

| 21   | JTAG_EN    | L                |                           | JTAG Enable in, this pin needs to be high for Boundary Scan use |

| 22   | DNC        |                  |                           | Do Not Connect                                                  |

| 23   | SCS_N      |                  | Constant drive            | Serial chip select from host (input)                            |

| 24   | VDD_1.8    |                  |                           | See below                                                       |

| 25   | GND        |                  |                           | Ground                                                          |

| 26   | UART_RX    | Н                |                           | Debug Serial in                                                 |

| 27   | UART_TX    |                  |                           | Debug Serial out                                                |

| 28   | GND        |                  |                           | Ground                                                          |

| 29   | VDD_3.3    |                  |                           | 3.3V Power                                                      |

| 30   | GND        |                  |                           | Ground                                                          |

| 31   | VDD_1.8    |                  |                           | See below                                                       |

| 32   | SDO        |                  |                           | Serial data out to host                                         |

| 33   | INT_NX     |                  | Pull-up                   | Interrupt to host (output)                                      |

| 34   | SCK        |                  | Constant drive            | Serial clock in from host                                       |

| 35   | SDI        |                  | Constant drive            | Serial data in from host                                        |

| 36   | GND        |                  |                           | Ground                                                          |

#### Notes:

- 1. VDD\_1.8 is an internally used supply rail. **DO NOT USE** these pins to drive other components.

- 2. Signals that note "Constant drive" must either be constantly driven by the host, or have a pullup or pulldown in case the host is likely to tri-state the signal during power down modes. The constant drive is used to ensure defined operation of the part and to minimize leakage current during low power modes.

- 3. RES is used as write-protect for the internal module SPI Flash. For production use, this pin should be pulled low. Host control will enable in-field FLASH updates.

# 4. Package Information

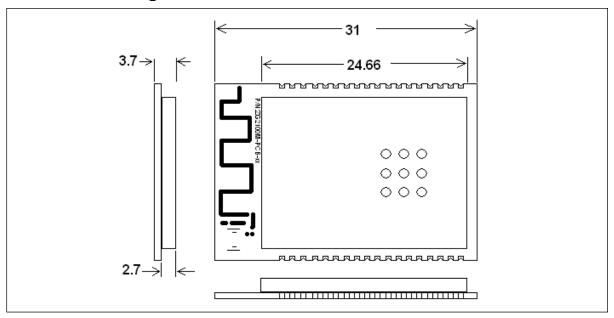

# 4.1 Module Drawing

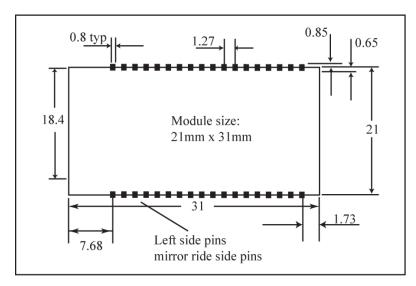

Figure 10: ZG2100M Module Physical Dimensions

All measurements are in millimeters. Tolerances for measures 0-10 mm is  $\pm$  0.05 mm.

Tolerances for measures 10-50 mm is +/- 0.1 mm

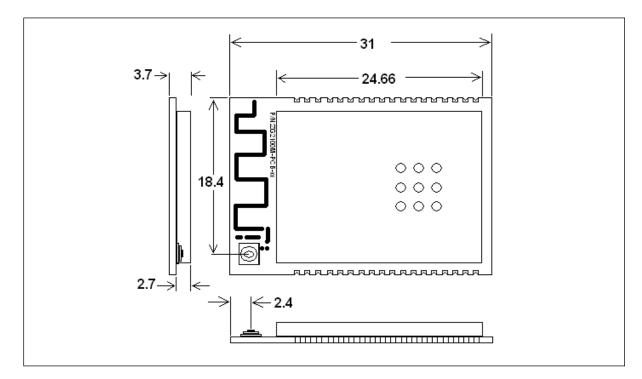

Figure 11: ZG2101M Module Physical Dimensions

All measurements are in millimeters. Tolerances for measures 0-10 mm is +/- 0.05 mm.

Tolerances for measures 10-50 mm is +/- 0.1 mm

Figure 12: ZG2100M/ZG2101M Module Layout Pad Dimensions

# 4.2 Module Layout Guidelines

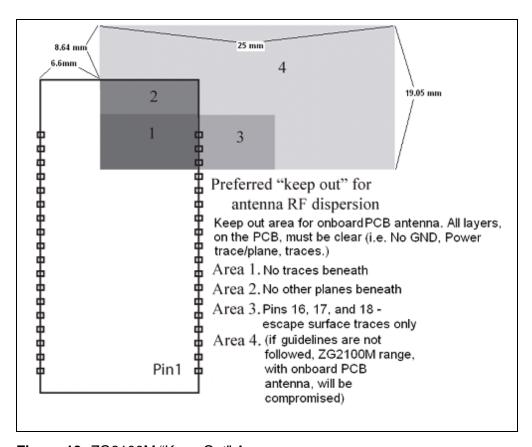

Figure 13: ZG2100M "Keep Out" Areas.

In addition to the guidelines in Figure 13, note the following suggestions: ZG2100M and ZG2101M

- Bypass capacitors for VDD\_3.3 should be as close as possible.

- Do not route any nets to VDD\_1.8

- Do not use VDD\_1.8 to source any external nets.

- Never place the antenna very close to metallic objects.

- The external antennas need a reasonable ground plane area for antenna efficiency.

- ZG2100M onboard PCB antenna specific

- Do not use a metallic or metalized plastic for the end product enclosure.

- Keep Plastic enclosure 1cm min height above the ZG2100M PCB antenna while maintaining the keep-out area, as shown in Figure 13.

# 4.3 Module Use Schematic

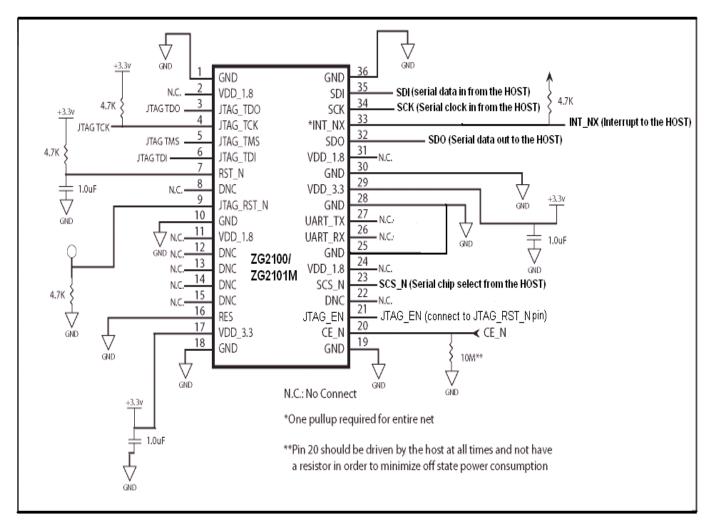

Figure 14: ZG2100M/ZG2101M Module Use Schematic.

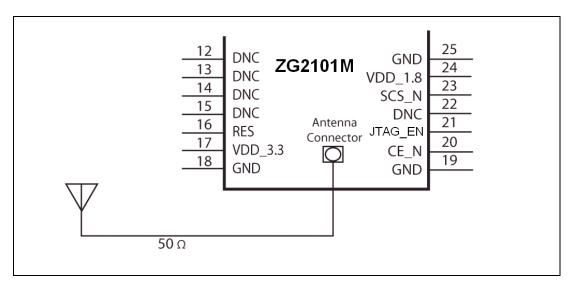

Figure 15: ZG2101M Antenna Connector/RF port diagram

#### Other Notes:

- 1. If RST\_N is always driven by the HOST, the RC circuit is not needed on this pin.

- 2. RES is used as write-protect for the internal module SPI Flash. For production use, this pin should be pulled low. Host control will enable in-field FLASH updates.

- 3. It's recommended to connect UART\_RX/TX (pins 26 and 27) to surface mount test points or header points, on the board, for optional connection to Hyperterminal for debugging purposes. Otherwise, they can be left as No Connects.

- 4. Ensure the HOST always drives the SPI port, even when not in use; otherwise, put 4.7K pull ups, to VDD\_3.3, on SDI, SCK, and SCS\_N.

DS70624A – page 22 © 2010 Microchip Technology

# 5. Electrical Characteristics

#### Absolute Maximum Ratings:

| Rating                   | Min    | Max     |

|--------------------------|--------|---------|

| Storage Temperature      | -40C   | +125C   |

| 3V supply (VDD_3.3)      | 0V     | 4.2V    |

| VDD_3.3                  |        | 0.5mSec |

| SDI, SCS_N, and SCK pins | -0.3 V | 5.5 V   |

#### **Recommended Operating Conditions:**

| Operating Condition                         | Min   | Тур  | Max   |

|---------------------------------------------|-------|------|-------|

| Ambient Temperature Range, commercial parts | 0C    |      | +70C  |

| 3V supply (VDD_3.3) – with FCC and IC cert  | 2.70V | 3.3V | 3.63V |

| 3V supply (VDD_3.3) – for ETSI cert         | 2.80V | 3.3V | 3.63V |

| 3V supply (VDD_3.3) – for Japan cert        | 2.97V | 3.3V | 3.63V |

# 5.1 Power Consumption

Nominal conditions: 25C, VDD\_3.3=3.3V

| Power Conservation Modes                                                               | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------------|-----|-----|-----|------|

| Hibernate, CE_N=3.3v                                                                   |     | 0.1 |     | uA   |

| Sleep                                                                                  |     | 250 |     | uA   |

| Standby (transitional power state)                                                     |     | 10  |     | mA   |

| Core Supply                                                                            | Min | Тур | Max | Unit |

| Rx On, Receive Irx @ -83dBm with 2Mb/Sec. modulated signal input power at antenna port |     | 85  |     | mA   |

| Tx On, Transmit Itx, +0dBm                                                             |     | 115 |     | mA   |

| Tx On, Transmit Itx, +10dBm                                                            |     | 154 |     | mA   |

#### **Electrical Characteristics Notes:**

- 1. If VDD\_3.3V supply takes longer than Maximum ramp up time, then CE\_N or RST\_N (held in active states; CE\_N=3.3V or RST\_N=0V) must be used to delay module boot up until VDD\_3.3 is within operating conditions range.

- 2. For Rx On, RX chain is fully ON.

# ZG2100M/ZG2101M

- 3. For Tx On, Pout= 0dBm (measured at antenna); 2Mb/Sec. modulated signal

- 4. For Tx On, Pout= +10dBm (measured at antenna); 2Mb/Sec. modulated signal

- 5. 3.3V Current Consumption values represent Typical Peak currents, and the measured currents conditions were done with 85% duty cycle modulated signal. WiFi applications typically operate in less than 85% TX duty cycle. Tx is dependent on such criteria as transmit power setting, and transmit data rate and bandwidth being used. Rx is affected by connectivity distance.

- 6. All characteristics in this specification are for commercial temperature rated parts only.

- 7. Operation in EU and/or Japan over extended voltage range of 2.7V to 3.6V will require additional certification testing by customer. The module is capable of this operation.

- 8. While 3.63V is the maximum operating voltage, the module will detect an overvoltage condition at 4.2V and disable the RF Transmit function. This is an RF Certification behavior pertaining to disabling transmission in unforeseen overvoltage conditions.

- 9. Listed Absolute Maximum Ratings are not meant for functional operation. Operation at these levels is not guaranteed, and may reduce the operating life of the component.

DS70624A – page 24 © 2010 Microchip Technology

# 6. Radio Characteristics

Nominal conditions: 25C, VDD\_3.3=3.3V

| Frequency range | Min  | Max  | Unit |

|-----------------|------|------|------|

| F_LO            | 2412 | 2484 | MHz  |

# 6.1 Transmitter 2.4 GHz Band

Nominal conditions: 25C, VDD\_3.3 =3.3V, Flo=2437MHz; 2Mb/Sec. modulated signal duty cycled at 95% measured at recommended single ended balun output (see Figure 8).

| TX                                                   | Min  | Тур | Max | Unit |

|------------------------------------------------------|------|-----|-----|------|

| Average Pout (Transmit spectrum mask Compliant)      |      | +10 |     | dBm  |

| Average Pout gain step resolution from +5 to +10 dBm |      | 0.5 |     | dB   |

| Average Pout gain step resolution from -5 to +5 dBm  |      | 1.0 |     | dB   |

| Average Pout settled variation                       | -0.5 |     | 0.5 | dB   |

# 6.2 Receiver 2.4 GHz Band

Nominal conditions: 25C, VDD\_3.3 =3.3V, Flo=2437MHz; measured at recommended single ended balun input (see Figure 8).

| RX                                            | Min | Тур | Max | Unit |

|-----------------------------------------------|-----|-----|-----|------|

| RX Min Input Level Sensitivity, 1Mbps, 8% PER |     | -91 |     | dBm  |

| RX Min Input Level Sensitivity, 2Mbps, 8% PER |     | -88 |     | dBm  |

| RX Max Input Level (Power), 1Mbps, 8% PER     |     | -4  |     | dBm  |

| RX Max Input Level (Power), 2Mbps,8% PER      |     | -4  |     | dBm  |

# 7. Digital Electrical Characteristics

Nominal conditions: 25C, VDD\_3.3=3.3V

| Characteristic                            | Min  | Тур  | Max | Unit |

|-------------------------------------------|------|------|-----|------|

| VIL (Input Low Voltage)                   | -0.3 |      | 0.8 | V    |

| VIH (Input High Voltage)                  | 2    |      | 5.5 | V    |

| VOL (Output Low Voltage)                  |      |      | 0.4 | V    |

| VOH (Output High Voltage)                 | 2.4  |      |     | V    |

| IOL (Low Level Output Current @ VOL Max)  |      | 8.5  |     | mA   |

| IOH (High Level Output Current @ VOH Min) |      | 15.4 |     | mA   |

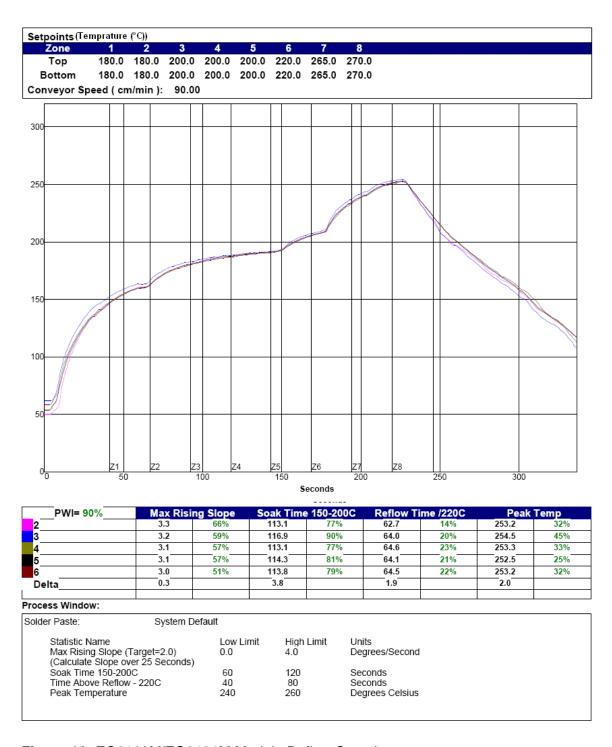

# 8. Module Reflow Profile

Figure 16: ZG2100M/ZG2101M Module Reflow Setpoints

# 9. Ordering Information

| Device<br>Description | Comment                                           | Ordering Number |

|-----------------------|---------------------------------------------------|-----------------|

| Module                | Commercial grade with PCB antenna                 | ZG2100MC        |

| Module                | Commercial grade for use with an external antenna | ZG2101MC        |

# 10. Regulatory Notes

#### Federal Communication Commission Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

FCC Caution: To assure continued compliance, (example – use only shielded interface cables when connecting to computer or peripheral devices). Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment. This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### **IMPORTANT NOTE:**

#### **FCC & IC Radiation Exposure Statement:**

This equipment complies with FCC & IC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20cm between the radiator & your body.

This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter. This device is intended only for OEM integrators under the following conditions:

- 1) The antenna must be installed such that 20 cm is maintained between the antenna and users, and

- 2) The transmitter module may not be co-located with any other transmitter or antenna. As long as 2 conditions above are met, further transmitter test will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed (for example, digital device emissions, PC peripheral requirements, etc.).

IMPORTANT NOTE: In the event that these conditions cannot be met (for example certain laptop configurations or co-location with another transmitter), then the FCC & IC authorizations are no longer considered valid and the FCC & IC IDs cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining separate FCC & IC authorizations.

# ZG2100M/ZG2101M

#### **End Product Labeling**

This transmitter module is authorized only for use in device where the antenna may be installed such that 20 cm may be maintained between the antenna and users (for example access points, routers, wireless ADSL modems, and similar equipment). The final end product must be labeled in a visible area with the following: "Contains FCCID: W7OZG2100-ZG2101 & IC: 8248A-G21ZEROG".

#### IC Certification — Canada

The labeling requirements for Industry Canada are similar to those of the FCC. A visible label on the outside of the final product must display the IC labeling. The user is responsible for the end product to comply with IC ICES-003 (Unintentional radiators)

#### Manual Information That Must be Included

The user's manual for end users must include the following in-formation in a prominent location. IMPORTANT NOTE: To comply with FCC & IC RF exposure compliance requirements, the antenna used for this transmitter must be installed to provide a separation distance of at least 20 cm from all persons and must not be co-located or operating in conjunction with any other antenna or transmitter.

#### Other notes:

ZeroG modules have been built or under development for near body exposure applications. The 20cm statement is a standard note because absorption rate testing (commonly known as SAR or Specific absorption rate) is not modularly transferable for FCC/IC. Thus, if a radio is being used against the body, the end user is still responsible to test for regulatory near body exposure testing (for USA, please refer to the following):

FCC Part 1.1037

FCC Part 2.1091 Mobile Devices

FCC Part 2.1093 Portable Devices

FCC Part 15.247 (b) (4)

# 11. Revision History

Revision A (March 2010)

Revision A includes document updates from version 1.0 to 2.4.

# WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

#### **Corporate Office**

2355 West Chandler Blvd.

Chandler, AZ 85224-

6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.c

om

Web Address: www.microchip.com

#### **Atlanta**

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

#### **Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

#### Chicago

Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

#### Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

#### Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

#### **Detroit**

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

#### Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

#### Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

#### Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

#### **Toronto**

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

#### **Asia Pacific Office**

Suites 3707-14, 37th Floor

Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

#### Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

#### China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

#### China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

#### China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

# China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

#### China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

#### China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

#### China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

#### China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

#### China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

#### China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

#### China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

#### China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

#### India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

#### India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

#### India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-

#### 1513

**Japan - Yokohama** Tel: 81-45-471- 6166

Fax: 81-45-471-6122

#### Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

#### Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

#### Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

#### Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

#### Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

#### Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

#### Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

#### Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

#### Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

#### Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

#### Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

#### Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

#### **France - Paris** Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 Germany - Munich

#### Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

#### Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

#### Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

#### Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **UK - Wokingham**

#### Tel: 44-118-921-5869 Fax: 44-118-921-5820